TSMC vs. サムスン vs. インテル: TSMC第1四半期決算に向けた2nm覇権争い

TSMCは第1四半期に売上高・純利益ともに過去最高を記録し、今後は2nmプロセスの歩留まりと量産立ち上げ速度が注視される。2nmプロセスはトランジスタ密度向上と高速化・低電力化を実現し、TSMC、サムスン、インテルが激しく競争している。TSMCは2025年末までに2nm量産開始、2026年後半には性能強化版N2P、A16プロセスの生産を目指す。歩留まり、増産立ち上がり、コスト面でTSMCが優位に立つ一方、インテルは裏面電源供給技術で先行している。TSMCはアップル、NVIDIAといった主要顧客との強固なエコシステムにより、2nm市場で絶対的優位を確立している。

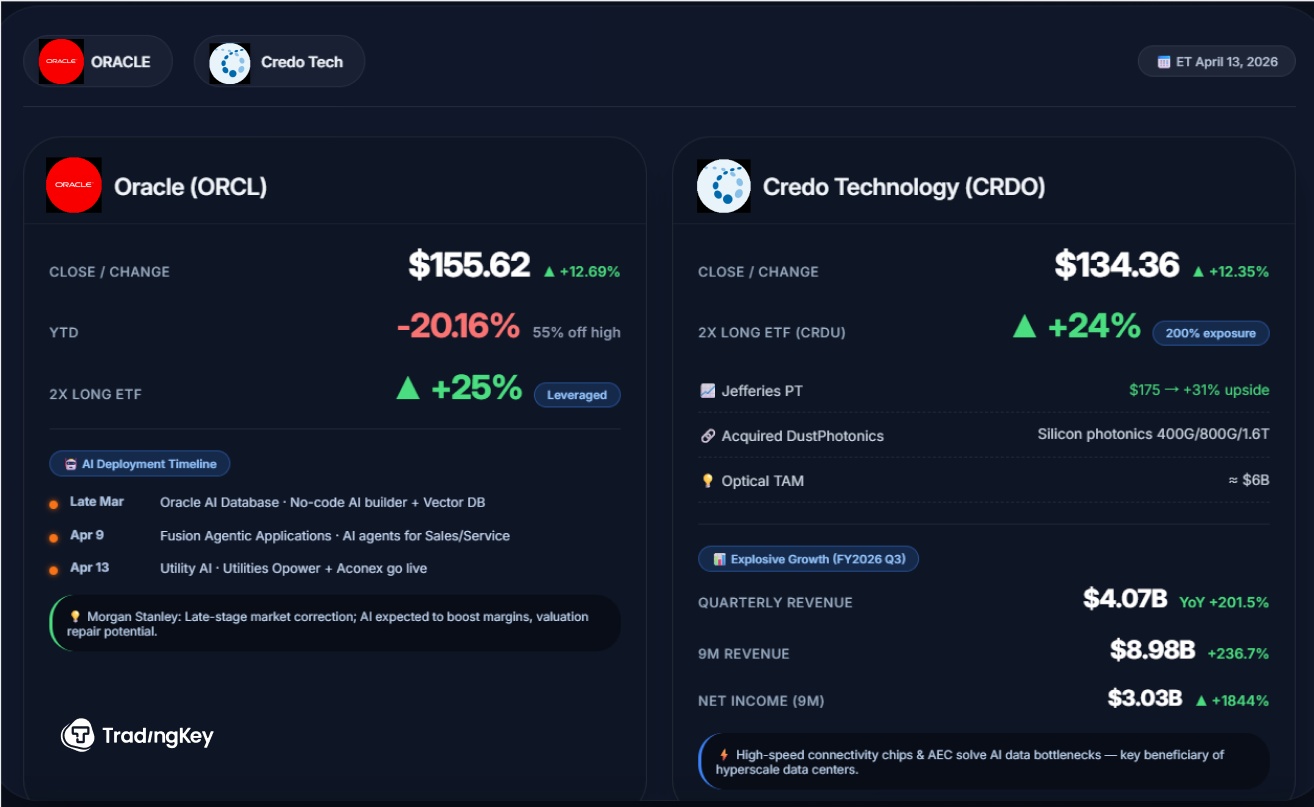

TradingKey - TSMC (TSM) TSMCは今週木曜日(4月16日)に第1四半期決算を発表する。同社が既に発表した第1四半期の売上高は前年同期比約35%増の1兆1340億台湾ドル(約356億ドル)と過去最高を記録し、初めて1兆台湾ドルの大台を突破した。

さらに、LSEGはTSMCの今四半期の純利益が50%増の5426億台湾ドル(約171億ドル)になると予測しており、実現すれば4四半期連続で過去最高益を更新することになる。

アナリストは、決算説明会で注視すべき最も重要な技術指標は2ナノ(nm)プロセスの歩留まりと量産立ち上げの速度であり、これがTSMCが他の半導体大手に対するリードを広げるための重要な主戦場になると指摘している。

2nmプロセスとは何か:TSMC、サムスンおよびインテルとの攻防

2nmプロセス(N2プロセス)は、半導体製造における特定のノードである。コンポーネントの実際の物理的寸法が2nmであることを単純に意味するものではないが、このプロセスは現在量産可能な精密構造の頂点を象徴している。

現在主流の3nmプロセスと比較して、2nmはトランジスタ密度を向上させる。同一のワークロードにおいて、後者はより高速、あるいはより電力効率に優れている。

現在、TSMCやサムスン電子の2nmプロセス、およびインテルの (INTC) 18A(実質的な1.8nmプロセス)は、名称こそ異なるものの、同等の性能水準に位置している。

TSMC第1四半期決算:2ナノの歩留まりと量産拡大のペースに焦点

2025年末までに、TSMCの2nmプロセスは量産段階に入り、新竹宝山工場が主にアップル (AAPL) をはじめとする主要顧客の初期需要に対応する一方で、高雄工場の生産能力も急速な立ち上げが続いている。

第1世代の2nmプロセスをベースにした性能強化版「N2P」は、同一消費電力で速度を約5%向上させることが可能で、2026年後半の生産開始を見込む。N2Pよりもさらに先進的なのが、1.6nmプロセスに相当するオングストロームレベルのチップ「A16」であり、TSMCの技術ロードマップにおける新たな大きな飛躍を象徴している。N2Pと比較して、A16は同一電圧で8〜10%高速化される。このプロセスも2026年後半に生産が予定されている。

現在、これら3つのノードの中で最も注目すべきは2nmプロセスである。TSMCとその競合であるサムスンやインテルが、この技術ノードで激しい競争を繰り広げているためだ。2nmプロセスは、現時点で最も迅速な商業化の可能性を秘めた最先端技術である。

今回の決算説明会では、歩留まりとランプアップ(増産)の傾斜に焦点を当てるべきだ。それらの量産成熟度が、2026〜2027年のTSMCの平均販売価格(ASP)の軌道を決定するためである。歩留まりとは全生産量に占める良品チップの割合を指し、歩留まりの向上は廃棄チップの減少とコスト低下を意味する。ランプアップの傾斜は、試験生産から大規模量産への移行過程における生産能力の拡大速度を指し、これが急であるほど迅速な市場獲得が可能になる。

これら2つの指標は、すでに量産に入っている新竹および高雄工場の月間生産能力レベルに反映されている。2nmの単価が現行の3nmより約30〜50%高いことを踏まえ、TSMCが生産能力のリードを維持しコストを削減できれば、2nmプロセスの量産成熟度が2026〜2027年のTSMCの平均販売価格の動向を直接左右することになる。

分析によると、2nmプロセスはTSMCの歴史の中で最も製品寿命の長いノード世代になると予測されている。技術的観点から、2nmは物理的限界に近づいており、短期間での突破は困難である。その結果、2nmファミリー(N2PおよびA16を含む)は量産チップの中で最高の性能を提供することになり、この分野におけるTSMCの優位性により、売上高総利益率は60%超で安定する可能性がある。

TSMC対サムスン対インテル:なぜTSMCが2nm開発競争で優位に立つのか

歩留まり:TSMCが圧倒的なリードを維持

2025年初頭の情報によると、TSMCの2nm歩留まりは60%から70%の間で安定している。

4月13日の最新報告によると、サムスンの2nm歩留まりは約55%にとどまり、TSMCに約10ポイントの差をつけられている。これは重要なファブレス企業からの受注を競うために必要な水準に達していない。業界関係者は、性能選別や後工程のパッケージング・テストでの損失を考慮すると、サムスン電子の最終製品ベースの2nm歩留まりはわずか40%にまで低下すると指摘しており、同社の2nmプロセスが成熟には程遠いことを示唆している。

2025年中頃の情報では、インテルの18Aプロセスの初期量産歩留まりは55%~60%に過ぎない。インテルのCFOは以前、歩留まりが商業的に許容可能なコスト水準に達するのは2026年末になり、業界標準の水準に達するのは2027年以降になるとの見通しを明らかにしている。

増産の立ち上がり(ランプアップ):TSMCが最も急なカーブを描く

アップルによる膨大なチップ需要に後押しされ、TSMCは量産開始から短期間で月産数万枚のウェハー規模まで拡大する必要がある。その結果、同社の2nm増産の立ち上がりは現在、業界で最も急ピッチとなっている。

インテルは現在18Aに注力しているが、今年の18Aの受注は主に「Panther Lake」プロセッサなどの自社製品向け需要が中心である点は注目に値する。したがって、その増産の立ち上がりは自社製品の市場での評価に大きく左右され、TSMCと比較して緩やかになると予想される。

3社の中で、サムスンは最も深刻な問題である「顧客離れ」に直面している。最新の報告によると、サムスンの2nm歩留まりは昨年の20%から現在の60%まで改善したものの、クアルコム (QCOM)は、サムスンの生産能力の制約を理由に、次世代Snapdragon 8シリーズのフラッグシップチップの注文をTSMCに継続して発注している。大規模な受注の裏付けがないため、サムスンの増産の立ち上がりも比較的平坦になると予想される。

コスト:TSMCが最低コストと最高粗利益率を誇る

TSMCは、卓越した歩留まりと膨大な出荷量により、2nmのコストを押し下げる能力が最も高いメーカーとして広く認識されている。高い歩留まりは廃棄の減少を意味し、大量生産は設備や装置の減価償却費のより効率的な回収を可能にする。しかし、顧客にとってはTSMCの製品が最も高価であり、結果として同社に最高の粗利益率をもたらしている。

サムスンは主にサプライチェーン全体の垂直統合に依存している。同社は通常、TSMCよりも魅力的なファウンドリ価格を顧客に提示する。これは主に、サムスンが設計、ファウンドリサービスからメモリ、パッケージングまでを一貫して手がけており、内部での利益調整によってチップ全体のコストを下げることができるためだ。

現在、インテルは主な顧客が内部であるため、ファウンドリ事業の利益率にはあまり関心を払っていない。これによりファウンドリ利益率の交渉を回避でき、製品全体の最終的な粗利益率のみに集中することが可能となっている。

技術的マイルストーン:インテルがリード

TSMCはA16プロセスで裏面電源供給を導入したが、インテルはこの技術のパイオニアであり、18Aノードですでに完全に統合している。

TSMCは現在のベースとなる2nmプロセスでは裏面電源供給を採用していない。つまり、特定のハイパフォーマンス・コンピューティング(HPC)のシナリオにおいては、インテルのアーキテクチャがエネルギー効率の面で優位に立つ可能性がある。

顧客エコシステム:TSMCの絶対的優位

現在、TSMCは2nm市場で最も引く手あまたの存在である。アップルが初期生産能力の大半を確保しているだけでなく、エヌビディア (NVDA)も次世代AIアーキテクチャにおいてTSMCと深く連携している。

サムスンはTSMCとの競争に苦戦しているものの、テスラ (TSLA)から昨年7月に164億ドル規模の受注を獲得し、2nmプロセスを用いてテスラのAI6チップを生産することになった。

このコンテンツはAIを使用して翻訳され、明確さを確認しました。情報提供のみを目的としています。